Recent News

- Exploring New Frontiers in Computing: Expert Lecture by Dr Aditya Japa July 23, 2025

The Department of Electronics and Communication Engineering (ECE) at SRM University-AP, Amaravati recently hosted a thought-provoking guest lecture on “Approximate Computing and Hardware Security: Opportunities and Risks”, featuring Dr Aditya Japa, a renowned researcher and faculty member at the School of Computing, Engineering and Intelligent Systems, Ulster University, UK.

The Department of Electronics and Communication Engineering (ECE) at SRM University-AP, Amaravati recently hosted a thought-provoking guest lecture on “Approximate Computing and Hardware Security: Opportunities and Risks”, featuring Dr Aditya Japa, a renowned researcher and faculty member at the School of Computing, Engineering and Intelligent Systems, Ulster University, UK.The session organised by Dr Ramesh Vaddi, Associate Professor, Department of ECE brought together over 110 participants, including faculty, PhD scholars, and UG/PG students, eager to gain insights into the evolving paradigms of energy-efficient and secure hardware design.

Dr Japa holds a Ph.D. in Electronics and Communication Engineering from Dr SPM IIIT Naya Raipur, India, with specialisation in emerging technologies for hardware security. His illustrious academic journey includes significant research contributions at Queen’s University, Belfast, and a published book titled “Introduction to Microelectronics to Nanoelectronics: Design and Technology.” His current work at Ulster University revolves around hardware and system security, particularly in Physical Unclonable Functions (PUFs), True Random Number Generators (TRNGs), and security strategies for approximate computing.

Key Highlights of the Lecture

Approximate computing is fast emerging as a compelling approach for building high-performance and energy-efficient systems, especially for error-tolerant applications like multimedia processing, AI, and big data analytics. However, this paradigm also introduces unique security challenges and opportunities, as explored in-depth by Dr Japa.

Key points covered included:

- Threat Models in approximate circuits and memory architectures such as DRAM and SRAM, revealing vulnerabilities to side-channel attacks, reverse engineering, and hardware Trojans.

- How approximate hardware, despite risks, can serve as a platform for resource-efficient security primitives.

- Security through approximation: Leveraging simplified circuits for information hiding and obfuscation, maintaining security with significantly reduced computational cost.

- Future research directions including secure-by-design architectures, cross-domain applications, and standardised benchmarking tools.

The session aimed to expose students and researchers to state-of-the-art advancements in hardware security and to encourage critical thinking around the duality of risk and opportunity in approximate computing. Participants walked away with a deeper understanding of:

- Designing systems that are both efficient and resilient.

- Emerging countermeasures against approximation-induced vulnerabilities.

- The strategic role of interdisciplinary research in addressing these challenges.

Recommendations for Further Action

- The event also sparked actionable recommendations for academia and industry:

- Develop approximation-aware threat models for various application domains.

- Design architectures that are secure by approximation.

- Invest in benchmarking and validation tools for secure approximate systems.

- Encourage cross-domain research in computing, security, and AI.

- Promote education and policy development in secure hardware design.

Events like these reflect SRM University-AP’s unwavering commitment to academic excellence, industry-relevant training, and research-led learning. The ECE department continues to serve as a platform for knowledge exchange and global collaboration, preparing students for the next generation of technological innovation.

Continue reading → - A Novel Cooperative Spectrum Sensing Method Based on MASSFormer June 26, 2025

In the digital era, enhancing wireless connectivity is vital for systems’ accurate and efficient functioning. Working on a smart system to catalyse seamless wireless connectivity, Dr Dimpal Janu, Assistant Professor from the Department of Electronics and Communication Engineering, has published a paper “MASSFormer: Mobility-Aware Spectrum Sensing using Transformer-Driven Tiered Structure” in the Q1 journal IEEE Communications Letters. She has developed a novel cooperative spectrum sensing method based on MASSFormer that uses artificial intelligence, specifically a transformer model, to decide when to use a communication channel without causing interference.

Abstract

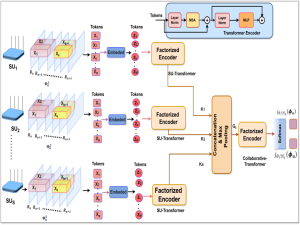

We develop a novel mobility-aware transformer-driven tiered structure (MASSFormer) based cooperative spectrum sensing method that effectively models the spatio-temporal dynamics of user movements. Unlike existing methods, our method considers a dynamic scenario involving mobile primary users (PUs) and secondary users (SUs) and addresses the complexities introduced by user mobility. The transformer architecture utilises an attention mechanism, allowing the proposed method to model the temporal dynamics of user mobility by effectively capturing long-range dependencies. The proposed method first computes tokens from the sequence of covariance matrices (CMs) for each SU. It processes them in parallel using the SU-transformer to learn the spatio-temporal features at the SU-level. Subsequently, the collaborative transformer learns the group-level PU state from all SU-level feature representations. The main goal of predicting the PU states at each SU-level and group-level is to improve detection performance even more. The proposed method is tested under imperfect reporting channel scenarios to show robustness. The efficacy of our method is validated with simulation results that demonstrate its higher performance compared to existing methods in terms of detection probability Pd, sensing error, and classification accuracy (CA).

Practical Implementation of Research

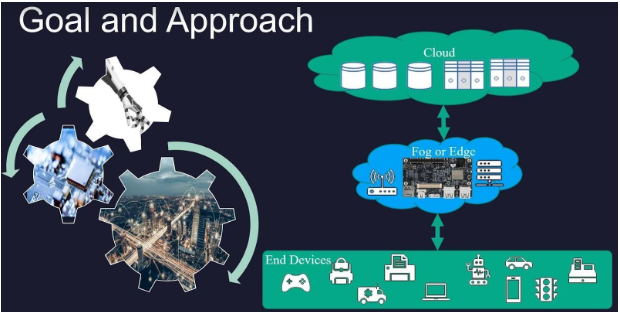

Smart cities & IoT Networks:

- MASSFormer enables intelligent spectrum sharing among a multitude of IoT devices in urban environments.

- It improves communication reliability in crowded and mobile settings, such as vehicular networks, smart traffic systems, or surveillance setups.

Social Implications of Research

MASSFormer is built to handle the mobility of users, which is essential in rural, remote, or developing areas where users often access the internet via mobile networks rather than fixed infrastructure. By enabling more efficient use of existing spectrum, the method helps extend internet access to remote and underserved regions, supporting education, healthcare, and economic development.

Future Research Plans

- Planning to develop hybrid models that blend classical detection with neural inference for improved interpretability and reliability.

- Use of federated learning so that SUs can collaboratively train models without sharing raw data.

Link to the article

Continue reading → - GAA-NSFET Biosensor for High-Sensitivity Label-Free Detection June 23, 2025

A cutting-edge research paper titled “Gate-All-Around Tree-Shaped NSFET-Based Biosensor: A High-Sensitivity Approach for Label-Free Biomolecule Detection” led by Dr M Durga Prakash, Associate Professor in the Department of Electronics and Communication Engineering, and Ms U Gowthami, PhD Scholar, has been published in the prestigious Q1 journal “Results in Engineering” with an Impact Factor of 6.0.

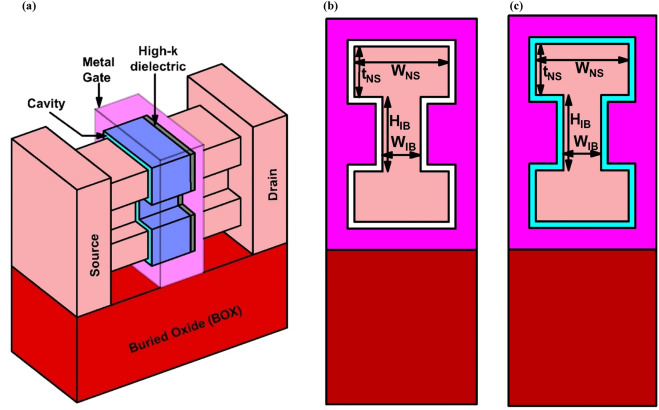

A cutting-edge research paper titled “Gate-All-Around Tree-Shaped NSFET-Based Biosensor: A High-Sensitivity Approach for Label-Free Biomolecule Detection” led by Dr M Durga Prakash, Associate Professor in the Department of Electronics and Communication Engineering, and Ms U Gowthami, PhD Scholar, has been published in the prestigious Q1 journal “Results in Engineering” with an Impact Factor of 6.0.This study presents a groundbreaking advancement in label-free biosensing technology by developing a highly sensitive biosensor. The device can detect extremely small biological molecules—such as proteins and DNA—without the need for traditional labeling methods that rely on fluorescent or radioactive tags. At the core of this innovation is a uniquely engineered transistor known as the Gate-All-Around Tree-Shaped Nanosheet Field-Effect Transistor (GAA-TS-NSFET). With its distinctive tree-like structure featuring multiple nanosheet branches, this advanced transistor design enables the detection of both charged and neutral biomolecules with exceptional sensitivity.

Abstract :

This paper proposes and investigates a label-free dielectrically modulated biosensor employing a Gate All Around Tree-Shaped Nanosheet Field Effect Transistor (GAA-TS-NSFET). The suggested biosensor’s excellent sensitivity to charged and neutral biomolecules is demonstrated by its electrical properties when evaluated under various biomolecule influences.A thorough sensitivity assessment is used to assess the sensing capabilities of the biosensors with various channel configurations. As indicators of biosensor sensitivity variation, we examine the subthreshold swing (SS), threshold voltage (Vth), and current switching ratio (Ion/Ioff). According to the findings, an additional channel acts as an interbridge, allowing the tree-shaped biosensor to attain the best sensitivity compared to biosensors based on NSFETs. Additionally, the article investigates how various spacer materials impact sensitivity. We also run several scenarios to see how different fill percentages affect the proposed biosensor’s sensitivity. The amount of biomolecules present determines its sensitivity. Finally, the suggested biosensor’s sensitivity is compared to other notable biosensing application efforts in a status map. The proposed GAA-TS-NSFET-based biosensor outperforms the previous works concerning Ion/Ioff sensitivity.

Practical Implementation of the Research

- Faster & Cheaper Diagnostics – Reduces reliance on expensive lab tests, making healthcare more accessible.

- Early Disease Detection – Could save lives by catching illnesses (like cancer or infections) at earlier stages.

- Less Invasive Testing – Since it doesn’t require labeling (no dyes or radioactive tags), it’s safer and simpler.

- Environmental Benefits – Could replace some chemical-based detection methods with electronic sensing, reducing waste.

Collaborations: School of Engineering, University of Warwick, Coventry CV4 7AL United Kingdom

Continue reading →

Fig. (a) 3-D view of GAATree-shaped NSFET-based biosensor; Transverse cross-sectional view of GAA Tree-shaped NSFET-based biosensor: (b) from source side and (c) from drain side.

- Accelerating SVM Computations Using an FPGA-Based Embedded System June 9, 2025

In a commendable stride toward advancing edge AI technology, Dr Swagata Samanta, Assistant Professor in the Department of Electronics and Communication Engineering along with B.Tech students Amrit Kumar Singha and Arnov Paul, have successfully filed and published a patent titled “A System for FPGA-based Acceleration of Support Vector Machine (SVM) Computations, and a Method Thereof” in Patent Office Journal.

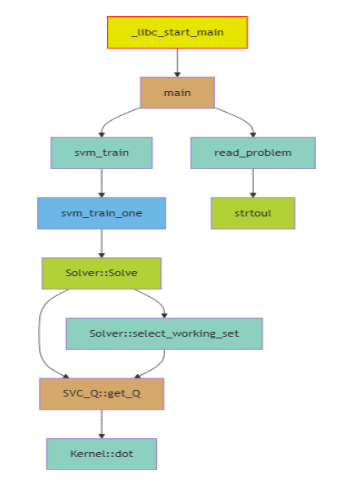

In a commendable stride toward advancing edge AI technology, Dr Swagata Samanta, Assistant Professor in the Department of Electronics and Communication Engineering along with B.Tech students Amrit Kumar Singha and Arnov Paul, have successfully filed and published a patent titled “A System for FPGA-based Acceleration of Support Vector Machine (SVM) Computations, and a Method Thereof” in Patent Office Journal.The patented system introduces a novel approach to speeding up machine learning algorithms specifically Support Vector Machines by implementing them on Field-Programmable Gate Array (FPGA)-based embedded systems. By harnessing the capabilities of Xilinx’s Vitis High-Level Synthesis (HLS), the team was able to develop a hardware-accelerated solution that dramatically enhances computational efficiency while simplifying the design process through C++-based abstraction.

Abstract:

By utilising the power and flexibility of FPGAs, the aim is to enhance the performance and efficiency of these compute-intensive tasks without delving into the intricate low-level hardware details. The approach involves implementing the fundamental concepts of SVM algorithms using the Vitis HLS design flow provided by Xilinx. Vitis HLS allows us to describe these algorithms at a higher level of abstraction using C++, enabling faster development and easier optimisation compared to traditional HDL- based designs.

By leveraging the capabilities of Xilinx Zynq-based embedded systems, we can efficiently accelerate these algorithms and improve overall system performance. GDS2 is a standard file format used for representing integrated circuit layouts, playing a crucial role in the physical design and fabrication of FPGAs by capturing the geometric and connectivity information of components such as logic blocks, interconnects, and I/O pads.

Proper GDS2 layout design is essential for ensuring manufacturability, optimising performance, maximising area utilisation, and maintaining signal integrity within an FPGA, taking into account physical constraints and design rules imposed by the fabrication process to minimise signal propagation delays, reduce power consumption, optimise timing, achieve higher density, minimise wasted space, and employ proper routing and shielding techniques to minimise crosstalk, signal reflections, and other signal integrity issues. By combining the power of HLS using Vitis with the Cadence GDS2 layout design, this project aims to accelerate SVM algorithms on FPGA-based embedded systems.

The use of Vitis HLS simplifies the development process and enhances productivity, while the GDS2 layout design ensures manufacturability, performance optimisation, efficient area utilisation, and signal integrity. This work showcases the potential of using FPGAs for hardware acceleration of machine learning algorithms, opening up new possibilities for embedded systems in various domains such as computer vision, natural language processing, and data analytics.

Implementation and Impact:

This work advances machine learning on FPGAs by optimising SVM algorithms for speed via parallel processing, supporting multiple ML models, and using Vitis HLS for efficient hardware-software co-design, while reducing power consumption and enabling scalability through multi-FPGA or hybrid systems; we’ll test in real-world IoT, automotive, and medical applications, compress models with pruning and quantisation, transition to ASICs for mass production, and develop standardised interfaces and on-device learning to enhance privacy and adaptability.

These advancements could make AI more accessible for low-cost medical diagnostics or smart devices in underserved areas, reduce carbon footprints through energy efficiency, boost economic growth through job creation, and improve safety in self-driving cars and smart homes. However, ethical design is crucial to prevent bias or misuse and ensure equitable benefits across society.

Future Directions:

Building on this foundation, the team plans to expand their architecture to support additional ML models, deepen hardware-software co-design efforts, and implement on-device learning for adaptive, privacy-preserving intelligence. Long-term goals also include transitioning to custom ASIC implementations for mass production and developing standardised interfaces to enhance system interoperability.

Continue reading → - SRM-AP Partners with Elevium to Offer Industry-Aligned Courses May 28, 2025

In a significant move to enhance skill-based learning through academia–industry collaboration, SRM University-AP, Amaravati, has entered into a strategic Memorandum of Agreement (MoA) with Elevium a division of Nanochip Skills Pvt. Ltd, a leading Bengaluru-based industry partner, to deliver cutting-edge, industry-aligned courses to students of the Department of Electronics and Communication Engineering (ECE).

In a significant move to enhance skill-based learning through academia–industry collaboration, SRM University-AP, Amaravati, has entered into a strategic Memorandum of Agreement (MoA) with Elevium a division of Nanochip Skills Pvt. Ltd, a leading Bengaluru-based industry partner, to deliver cutting-edge, industry-aligned courses to students of the Department of Electronics and Communication Engineering (ECE).This partnership bridges the gap between theoretical education and real-world industry requirements, particularly for ECE students. As part of the MoA, undergraduate ECE students from the 3rd to 7th semesters will have the opportunity to enroll in specialised, industry-aligned courses in VLSI, Embedded Systems, and Edge AI key domains shaping the future of the electronics sector.

Key Highlights of the Agreement:

Structured Course Delivery: One industry-aligned course per semester, each comprising 60 hours – delivered through a hybrid model of 40% offline and 60% online learning.

Enrollment Strategy: Designed for a minimum batch size of 120 students, with optional enrollment extended to students from other departments based on institutional discretion.Elevium will provide expert faculty from the industry, handle curriculum delivery, conduct assessments, and participate in curriculum review through Board of Studies meetings. SRM University-AP will facilitate access to classrooms, labs, and administrative support to integrate these courses seamlessly into the academic structure.

Student Evaluation and Curriculum Design:

Assessment methods and syllabus structures will be collaboratively developed and aligned with SRM-AP’s academic standards. The courses will include continuous evaluations and feedback mechanisms, with grading support from Elevium.

Placement and Career Support:

As part of its commitment, Elevium will extend comprehensive placement support including career counseling, guest lectures by industry experts, internship facilitation, and project guidance to enhance students’ employability.The primary goal of the MoA is to empower undergraduate students with hands-on learning aligned with current industrial practices and to facilitate their transition from classroom to the corporate world through structured and practice-driven academic modules.

The agreement was formally signed in the presence of esteemed dignitaries from both organisations, including Hari Krishnan Puravankara, CEO of Nanochip Group of Companies, Dr Manoranjan Kumar, Manager of university Programs at Nanochip Group of Companies, Dr Prem Kumar, Registrar, Prof. C V Tommy, Dean of SEAS, and other faculty members from the ECE department.

This collaboration exemplifies SRM-AP’s commitment to transforming education by integrating academic knowledge with industrial applications. Thus, students are empowered with real-world competencies that are crucial for tomorrow’s technology leaders.

Continue reading →